Chúng ta đã hồi hộp chờ đợi sự ra mắt của Core i7, hay còn gọi là Nehalem.

Chúng ta đã hồi hộp chờ đợi sự ra mắt của Core i7, hay còn gọi là Nehalem.Nhưng khi bộ vi xử lí này cuối cùng cũng ra mắt, nhiều người dùng lại cảm thấy thất vọng bởi họ đã đón chờ một sự kiện “đơn giản và rõ ràng” – Intel ra mắt bộ xử lý đầu tiên có mạch điều khiển bộ nhớ tích hợp. Quả thực cũng lấy làm lạ khi Intel lại mất nhiều thời gian đến vậy mới có thể theo kịp con đường mà AMD đã chọn, nhưng sau khi thu được kết quả kiểm định đã cho kết quả rất ấn tượng và tha thứ cho tất cả. Intel đã phát hành Core i7. Nhưng đây khác hẳn với một bộ vi xử lí “Core 2 có tích hợp thêm mạch điều khiển bộ nhớ” như chúng ta đã tưởng. . Trong phần đầu tiên của bài này, dành cho cấu trúc hệ điều hành mới của Intel, chúng ta sẽ tìm hiểu xem người dùng có thể chờ đợi gì từ bộ xử lý này mà không cần kiểm định, chỉ dựa trên các số liệu của nó. Còn phần thứ hai sẽ tập trung vào việc kiểm định lại sản phẩm này. ,

Trở lại lịch sử

Lý do chính khiến cho việc thiết kế nhân Nehalem chả liên quan gì đến ý định tích hợp bộ điều khiển bộ nhớ của Intel cả. Bởi thực ra mạch điều khiển bộ nhớ tích hợp chỉ là một cách để tăng tốc độ — mà Intel thì chẳng có lý do gì để tăng tốc bộ xử lý của mình: đối thủ chính của họ đã bị tụt lại rất xa và khó có thể bắt kịp trong một vài năm tới. Do đó sẽ là sai lầm rất lớn nếu bạn cho rằng Nehalem chỉ là một “Core 2 với mạch điều khiển bộ nhớ tích hợp.” Trong suy luận ban đầu của mình, lầm tưởng này đã khiến chúng ta đưa ra những kết luận sai lệch hoàn toàn. Vậy thì đâu là lý do chính đằng sau nhân mới này? Để hiểu rõ hơn, hãy cùng tìm hiểu người tiền nhiệm của nó là Core 2 (với một tư duy hoàn toàn tươi mới). Để hoàn thiện hơn chúng ta sẽ tiến hành phân tích cả về mặt kỹ thuật và lịch sử.

Trước khi có Core 2, Intel đã phải đối mặt với vấn đề gì? Hay cụ thể hơn là: khi Intel mới bắt đầu dự án Core 2 thì tình hình nội bộ công ty này ra sao? Nói một cách thẳng thắn, khi đó họ cực kỳ căng thẳng. Tất nhiên đây chỉ là một suy luận, nhưng cũng khá logic. Có thể Intel đã nhận ra rằng cấu trúc NetBurst đã đạt đến thời kỳ xuống dốc sớm hơn rất nhiều trước khi người dùng bình thường, hay thậm chí là các phòng kiểm định độc lập nhận ra điều đó. Cũng có thể ban PR và marketing của Intel đã tiết kiệm được một hai ngày gì đó, nhưng rõ ràng là thời gian này không phải là dài. Vậy nên rất logic khi nhận định rằng việc chuẩn bị cho Conroe khá vội vàng.

* Thậm chí cả bản mẫu đầu tiên của Intel Pentium M (nhân Banias) cũng được thiết kế trong một thời gian ngắn. Nhưng đây là bộ xử lý dành cho thiết bị di động. Và khi chi nhánh Intel tại Israel nhận được nhiệm vụ tạo ra một bộ xử lý thứ thiệt dành cho máy tính để bàn từ một bộ xử lý dành cho thiết bị di động (với một lịch trình dày đặc), mọi chuyện không hề dễ dàng chút nào.

Mặt khác, việc xem xét liệu sẽ mất bao nhiêu thời gian để thiết kế một nhân hoàn toàn mới (thậm chí phải khác biệt một cách lý tưởng so với cấu trúc cũ) và so sánh ngày bắt đầu thực hiện hai bộ xử lý Pentium D và Athlon 64 X2 với ngày bắt đầu thực hiện bộ xử lý đầu tiên dựa trên cấu trúc Core 2, chúng ta có thể dẫn đến một nhận định sau đây: rất có thể ban đầu Conroe không được xem như một nền tảng dành cho bộ xử lý đa nhân. Có lẽ chiến thuật ban đầu của họ là thế này: “hãy thiết kế một nhân xử lý đơn thật tốt, và nếu cần một bộ xử lý hai nhân, chúng ta chỉ cần ghép chúng lại.”Về lý thuyết, thiết kế của Conroe đã xác nhận giả thiết này, và thậm chí cả ý tưởng về Cache L2 chia sẻ cũng vậy (giải pháp tình thế này đã bị loại khỏi Nehalem, chỉ có L3 là cache chia sẻ). Hơn nữa: một số chi tiết (như công nghệ hợp nhất Macrofusion) cũng cho thấy một điều còn bất ngờ hơn: ban đầu Conroe không phải là một bộ xử lý 64 bit! Nhưng chúng ta sẽ nhắc lại chuyện này sau.

Do đó chúng ta gặp phải một nghịch lý kỹ thuật: các bộ xử lý 2 nhân và 4 nhân nhanh nhất của intel là Intel Core 2 Duo / Core 2 Quad lại cũ hơn nhiều so với các bộ xử lý đời cũ Athlon 64 X2 của AMD, chứ đừng nói đến Phenom X3/X4.

Thực ra mục tiêu chính của AMD và Intel trong việc thiết kế một CPU x86-64 hiện đại rất khác nhau: vốn tuân theo truyền thống, Intel tập trung vào việc thiết kế nhân xử lý tốc độ cao. Còn AMD – kẻ tiên phong, thì lại đem đến rất nhiều điều mới mẻ trong bộ xử lý Single-Core Athlon 64 , trong khi bộ xử lý này cần thêm nhiều nhân nữa (hay ít nhất là công nghệ đa xử lý ). Lần này bản năng của Intel đã không làm họ thất vọng: các bộ xử lý đáng lẽ đã trở thành những CPU Single-Core xuất sắc cuối cùng lại trở thành những sản phẩm đa nhân tốt nhất trong thời kỳ chuyển giao. Ví dụ như, việc phân tích kết quả kiểm định cho thấy một trong số những tính năng hữu ích nhất của cache L2 chia sẻ trong Core 2 chính là việc đưa gần như toàn bộ cache L2 vào một nhân trong mode Single-Core. Tuy nhiên, nếu nghĩ đến bản chất của quá trình chuyển giao này thì bạn sẽ nhận ra một kết quả rất khác: đó là thời điểm khi việc hỗ trợ công nghệ đa xử lý còn là một chủ đề nóng, nhưng các nhà phát triển phần mềm cũng chẳng nóng vội làm việc theo hướng này.

Nhưng quá trình chuyển giao này cũng sắp kết thúc, và bộ phận R&D của Intel cần phải trả lời câu hỏi: phải làm gì tiếp theo. Cấu trúc Core 2 là một mã thực thi rất mạnh (thực ra là mạnh nhất trong tất cả các giải pháp x86),những bộ xử lý hai nhân rất cân bằng, nhưng lại tạo ra nhiều vấn đề với những Model Quad-Core ( trong khái niệm Cấu trúc ), vậy điều gì sẽ đến tiếp theo đây? Điều gì sẽ xảy ra nếu thị hiếu thị trường bắt đầu lớn mạnh và nuốt chửng cả các bộ xử lý 8 nhân? AMD cũng đã trải qua một số khó khăn nhất định, trong đó có cả khó khăn về mặt kỹ thuật. Vì thế cũng có thể AMD sẽ trở thành công ty đầu tiên đưa ra giải pháp 8 nhân. Nhưng mặt khác, bộ xử lý Phenom hiện đại đã sẵn sàng cho 8 hoặc thậm chí là 16 nhân. Đó là lý do tại sao Intel lại cần một nhân mới, thậm chí là một cấu trúc mới – mạnh mẽ và được thiết kế để dành cho hệ thống đa nhân. Nehalem đã trở thành ứng dụng đầu tiên của cấu trúc này.

Những tính năng cơ bản của nền tảng mới

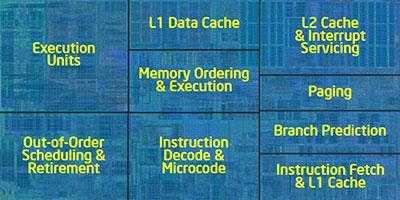

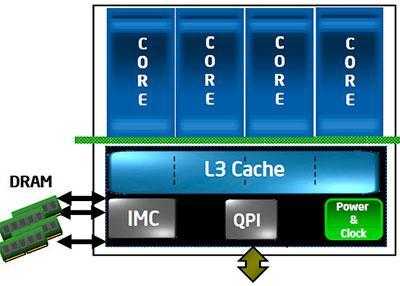

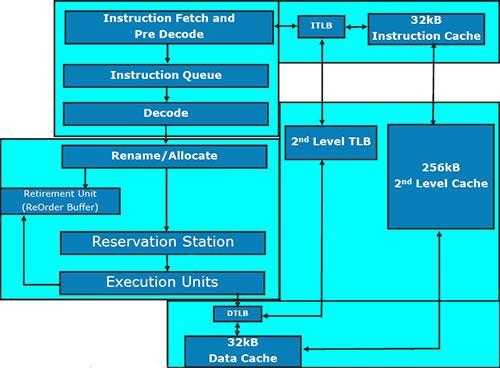

Như đã nói ở trên, tính năng chính của cấu trúc mới này nằm ở thiết kế module của nó. Theo quan điểm cách đây không lâu thì module chính là một CPU x86 đơn nhân cổ điển: nó chứa một nhân thực thi ( Excuting Core ) , cache L1 64KB chia làm hai phần bằng nhau cho dữ liệu ( Data ) và câu lệnh ( Instruction ) , và cache L2 256-KB. Chỉ cần chia đôi L1 là bạn đã có Pentium III Coppermine

Các thành phần khác gồm có:

1. Cache L3 chia sẻ

2. Mạch điều khiển bộ nhớ

3. Mạch điều khiển bus QPI (QuickPath Interconnect)

4. Mạch điều khiển bus PCI Express (chưa đưa vào ngay)

5. Bộ phận quản lí lượng tiêu thụ điện (PCU) và đồng hồ

6. Đồ họa tích hợp ( nó nằm cùng bên trong với CPU, nhưng trên một khuôn riêng).

Nhưng có thể đó không phải là một danh sách cố định, và rằng Core i7 có thể còn có chứa các thành phần khác. Danh sách các bộ phận cơ bản này giống như một tập hợp những mục tiêu gần nhất của Intel có liên quan đến việc phát triển cấu trúc – nó gồm một mạch điều khiển đồ họa tích hợp, hiện chưa có trong bất kỳ bộ xử lý Core i7 nào. Tất cả các thành phần trên đều có thể được kết hợp theo một cách bất kỳ, một số có thể bị loại ra và một số khác thêm vào. Mẫu thiết bị chúng ta sắp sửa kiểm định sau đây (Core i7 920) trông như thế này:

Như bạn đã thấy, nó gồm 4 nhân xử lý, một mạch điều khiển bộ nhớ DDR3 Triple-Channel tích hợp ( IMC ) , một mạch điều khiển QPI để liên lạc với chipset, và một module làm nhiệm vụ xác lập tần số cần thiết cho CPU và bộ phận quản lý điện năng. Mặt khác, đây chỉ là một trong số những tùy chọn có thể thực hiện từ model này.

Ví dụ như, nếu cấu trúc mới này được dùng trong bộ vi xử lý cho máy chủ — cũng chẳng hại gì khi tăng số nhân và mạch điều khiển QPI. Một CPU dành cho thiết bị di động có thể có ít nhân hơn để tiết kiệm điện, và QPI tôc độ cao thì có thể được thay thế bằng Điều khiển PCI Express . Xét về lý thuyết, L3 cũng có thể loại bỏ để giữ lại duy nhất những thành phần cơ bản: một nhân, một mạch điều khiển bộ nhớ, PCIe .

Do đó có vẻ Intel đã đạt được mục đích chính: công ty này đã có được một cấu trúc module với một số thành phần chính, có thể kết hợp lại để xây dựng một bộ xử lý hạng bình dân dành cho Nettop hoặc bộ xử lý đa nhân cho máy chủ. Và tất cả những điều này đều có thể thực hiện được với cùng những thành phần như nhau — đó mới là điều thú vị! Nhưng vẫn còn những thay đổi quan trọng khác. Hãy cùng tìm hiểu chúng.

Mạch điều khiển bộ nhớ tích hợp ( IMC )

Nhiều người cho rằng lý do rõ ràng nhất khiến Intel sử dụng mạch điều khiển bộ nhớ 3 kênh ( Triple-Channel ) trong Nehalem là bởi họ không muốn học theo cách thiết kế của AMD – họ không muốn vay mượn từ đối thủ. Tuy nhiên, sau khi nghiên cứu kỹ những rắc rối mà AMD gặp phải với mạch điều khiển bộ nhớ của họ, chúng ta sẽ hiểu rằng Intel đã quyết định đúng chứ không chỉ đơn thuần làm theo cảm xúc.

Chắc bạn còn nhớ AMD đã phải thiết kế lại mạch điều khiển bộ nhớ bên trong CPU khi chuyển từ bộ nhớ DDR-400 sang DDR2-800 bởi yêu cầu băng thông trong một số ứng dụng đã tiến sát mức tối đa. Do đó chắc chắn sẽ phải có một khe cắm bộ vi xử lý khác, một bo mạch chủ khác, và vô số những vấn đề mà người dùng phổ thông rất ghét (đặc biệt là những ai chỉ mong nâng cấp chiếc máy tính cũ của họ). Với ba kênh hỗ trợ DDR3-1333 (cho máy chủ có tên mã “Nehalem-EP”) hay DDR3-1066 (Nehalem cho máy tính để bàn) của mạch điều khiển bộ nhớ tích hợp trong Nehalem, có thể ý định của Intel là tránh việc như đã từng xảy ra với những bộ vi xử lí AMD trước kia như đã đề cập bên trên trong vài năm tới, hay nếu có thì cũng chỉ thay đổi không đáng kể. Ví dụ như, công ty này có thể thêm hỗ trợ bộ nhớ DDR3 tần số cao vào các CPU trong tương lai mà không cần nâng cấp bo mạch chủ.

Điều đáng quan tâm hiện nay là bản thân mạch điều khiển bộ nhớ. Theo Intel thì người dùng sẽ có được tốc độ trao đổi dữ liệu cao chưa từng có (32 GBps đạt được bằng cách nhân băng thông tối đa của DDR3-1333 với số kênh, vậy nên rõ ràng là chúng ta đang làm việc với một giá trị tối đa lý thuyết, không phải kết quả thực), thời gian trễ thấp (tại sao không? Mạch điều khiển bộ nhớ của Intel vốn có thời gian trễ rất thấp), và một việc “hăng hái sắp xếp lại yêu cầu.” Dựa trên tiêu đề này, có thể thấy đây không phải là tính năng thú vị nhất của mạch điều khiển mới. Tuy nhiên, ngoài ra cũng không có thêm thông tin đáng chú ý nào khác về công nghệ này.

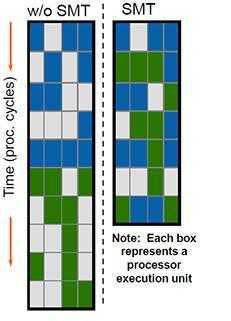

Công nghệ xử lý đa tuyến ( Simultaneous Multi-Threading )

Lại một lần nữa chúng ta bắt gặp công nghệ Hyper-Threading , vốn đã bị lãng quên sau khi bộ xử lý NetBurst bị bỏ dở. Công nghệ này giúp xây dựng nhiều nhân logic trên một nhân vật lý. Biểu đồ dưới đây có vẻ như lấy ra từ một bài thuyết trình cũ:

Cũng như Pentium 4, sự hồi sinh của công nghệ Hyper-Threading ( HT ) cũng phải hứng chịu một số “căn bệnh di truyền,” ví dụ như bộ nhớ đệm load/store/reorder (tải/lưu trữ/sắp xếp lại) bị chia đôi bởi hai nhân ảo. Vì thê khả năng hỗ trợ HT (đa tuyến) có thể làm giảm hiệu suất làm việc (nhưng cần chú ý rằng điều này hiếm khi xảy ra trong thực tế). Mặt khác, về lý thuyết thì HT của Nehalem phải làm việc tốt hơn nhiều so với trong Pentium 4 – không phải nhờ những cải tiến trong công nghệ này, mà chỉ bởi một số thành phần quan trọng trong công nghệ này “rộng hơn” nhiều so với trong Pentium 4 (chúng ta sẽ quay lại vấn đề này ở phần sau).

Bên cạnh đó chúng ta cũng bắt gặp nhiều thông tin trên mạng về việc Intel đã, bằng cách nào đó, tách đôi nhân vật lý và nhân logic trong Nehalem một cách không đều để giúp các lập trình viên có cơ hội nâng cấp phần mềm của họ lên công nghệ đa xử lý bằng loại CPU kích hoạt HT. Không hiểu sao điều này lại có thể thực hiện được – khi kích hoạt HT, tất cả các nhân sẽ trở thành ảo, và nhân đầu tiên được kích hoạt trên nhân vật lý sẽ không thể “ảo hơn” hoặc “không ảo bằng” nhân thứ hai, và tất cả các chương trình đều gặp vấn đề này. Do đó có thể có một cơ hội để tìm hiểu xem (bằng cách phân phối số nhân CPU?..) liệu các tuyến đã được thực thi trên các tuyến của cùng bộ xử lý vật lý hay trên nhân vật lý khác (trường hợp thứ hai có lợi hơn nếu xét về tốc độ tối đa đạt được trong một quy trình cho trước).

Xét trên tổng thể, việc hỗ trợ Hyper-Threading trên bộ xử lý 4 nhân dành cho máy tính để bàn có thể coi là một chuyển biến về ý thức hơn là nhằm tăng hiệu suất sử dụng CPU: chỉ có 0.5% các chương trình trên desktop là sử dụng được 8 nhân 1 cách hiệu quả, và các chương trình này chuyên nghiệp đến nỗi có khi người dùng phổ thông chưa từng nghe về chúng.

Nhân thực thi ( Execution Core )

Sử dụng từ “Execution Core“ có vẻ chính xác hơn “Computing Core” vì nó không chỉ làm nhiệm vụ tính toán mà còn giải mã câu lệnh. Ngoài ra, không phải tất cả các lệnh trong mã x86 đều là lệnh tính toán.

Phần lớn những thay đổi trong Core i7 so với Core 2 có thể được miêu tả như sau: “thêm vào một số, mở rộng một số khác.” Những cải tiến này rất dễ giải thích: quy trình sản xuất mới tạo ra nhiều Transistor hơn, vì thế không cần phải tiết kiệm Transistor làm gì. Còn bây giờ chúng ta sẽ tổng kết lại những thay đổi có lợi nhất:

Bộ phận mã hóa ( Decoder )

Thay đổi lớn nhất trong bộ phận giải mã có liên quan đến việc cải tiến công nghệ Macrofusion: nó chỉ hoạt động trong mode 32 bit, nhưng đã hỗ trợ tất cả các mode CPU, trong đó có mode 64-bit. Số lượng cặp lệnh được mã hóa trong mỗi chu kỳ bằng công nghệ này cũng đã tăng lên. Xét về lý thuyết thì bộ phận mã hóa Core i7 sẽ đạt hiệu suất (5 câu lệnh mỗi chu kỳ) nhiều lần hơn so với trong Core 2.

Xử lý chu kỳ

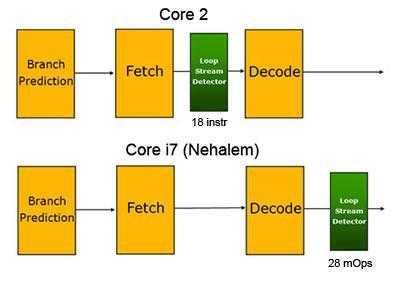

Loop Stream Detector, được thiết kế để lưu lại chu kỳ ngắn thay vì tải lại các chu kỳ này từ bộ nhớ Cache L1/L2, lần đầu xuất hiện trong các bộ xử lý Core 2. Trong Nehalem, bộ phận này hoạt động sau bộ phận giải mã, vì thế nó có được lệnh đã giải mã. Ý tưởng này xuât phát từ bộ vi xử lí Pentium 4, Trace Cache.

Dự đoán rẽ nhánh ( Branch Prediction )

Phần nhánh đã được tăng gấp đôi: giờ đây nó được chia làm 2 phần, một trong số đó có tốc độ dự báo nhánh cao hơn (có thể nó đã copy lại bộ phận dự báo trong Core 2), trong khi phần còn lại thì chậm hơn, nhưng có khả năng phân tích sâu sắc hơn kèm theo một Bộ đệm đủ lớn để dự đoán những nhánh mà phần nhanh hơn bỏ qua.

Intel cũng hứa hẹn rằng Return Stack Buffer(phụ trách các địa chỉ trả về chức năng) sẽ được mở rộng lên cả Renamed RSBnhư trong Penryn. Có điều trước đây bộ phận này vẫn thỉnh thoảng nhầm lẫn khi thực hiện những thuật toán phức tạp, nhưng giờ thì không.

Thực hiện lệnh ( Instruction Execution )

Những bộ phận phụ trách việc xử lý câu lệnh gần như không có thay đổi gì so với Nehalem. Do đó ta có thể đưa ra một kết luận đơn giản, nhưng không quá hiển nhiên rằng: trong những trường hợp Core 2 phải đối phó với việc câu lệnh và dữ liệu đã được lấy về trước ( Prefetch ) , giải mã và dự báo nhánh, thì các cải tiến đã nêu trong Core i7 không còn đem lại lợi thế nữa, và Core i7 sẽ có khả năng xử lý như Core 2.

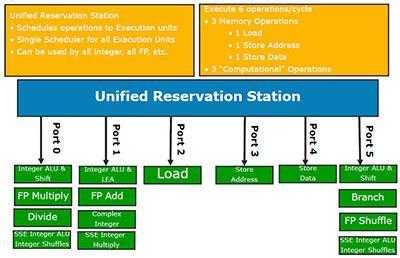

Tuy nhiên cũng có một số cải tiến trong việc hỗ trợ Hyper-Threading. Ví dụ như Reorder Buffer sắp xếp lại đã được mở rộng lên 128 vi lệnh, Reservation Station — lên 36 lệnh (trước là 32). Và những bộ đệm dữ liệu: khả năng tải tăng từ 32 lên 48, khả năng lưu trữ từ 20 lên 32. Lý do cũng rất đơn giản: để tăng số lượng câu lệnh và dữ liệu trong hàng thực thi, do đó tăng khả năng thực thi chúng cùng một lúc.

Tập lệnh mới (SSE4.2)

Như đã nói, Intel không thực hiện bất kỳ cải tiến đột phá nào trong thành phần thực thi của Nehalem nên việc bổ sung tập lệnh này là rất phù hợp: khác với SSE4.1 trong Penryn, SSE4.2 chỉ chứa 7 câu lệnh mới. Intel gọi hai trong số chúng là “Application Targeted Accelerators– Bộ gia tốc đích ứng dụng” tức là những lệnh có nhiệm vụ tăng tốc ứng dụng hơn là thuật toán. Một trong số chúng tính toán CRC32 để tăng tốc giao thức iSCSI. Còn lệnh thứ hai thì tính số lượng bit khác 0 trong một toán hạng, nó được dùng trong việc xử lý chung và trong các phần mềm nhận diện giọng nói. 5 lệnh còn lại có cùng một nhiệm vụ: tăng tốc thuật toán hoặc phân tích XML cú pháp. Bạn cũng thấy đấy, đây đều là các thay đổi khá trầm lặng!

Hệ thống Cache

Cách làm nước đôi này đã quá phổ biến trong Nehalem: các kỹ sư không chỉ tăng gấp đôi Bộ phận nhánh ( Branch Unit )mà còn cả TLB (Translation-Lookaside Buffer)nữa. Họ tiến hành cả hai việc theo cùng một cách: Bộ phận ( Unit ) thừa hưởng từ Core 2 sẽ được giữ nguyên (được mở rộng thêm một chút), còn cấp độ mới thứ hai được đưa vào trên TLB cũ – thậm chí nó còn lớn hơn (512 entry) và có nhiều chức năng hơn (TLB L2 có thể dịch địa chỉ trang với bất kỳ kích thước nào ) . Còn hỗ trợ những trang có kích thước bất kì mà hay được sử dụng trên bộ vi xử lý dành cho máy tính để bàn và tính năng này sẽ đi kèm với những ứng dụng máy chủ nặng . Và TLB lớn thì rõ ràng là một bước tiến mới lên SMT.

Tuy nhiên, hầu hết các thay đổi đều được giới thiệu trong hệ thống Cache chính, cụ thể là chức năng tương tác L1-L2 và cache L3 thêm vào Nehalem. Đầu tiên, L2 vẫn thuộc về một nhân nhất định chứ không chia sẻ. Còn L3 được chia sẻ giữa tất cả các nhân. Thứ hai, Intel đã điều chỉnh một chút đối với thời gian trễ của L1, còn độ trễ L2 — L1 thì cao hơn một chu kỳ so với trong Core 2, còn thời gian trễ của L2 thì thấp hơn đến 1.5 lần.

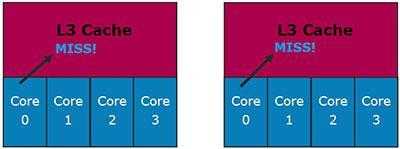

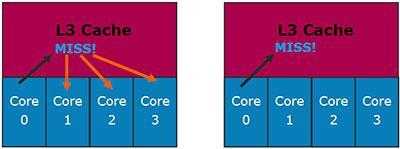

Nhưng tại đây chúng ta chủ yếu quan tâm đến L3. Cũng như L2 trong Core 2, đây là một Cache chia sẻ động. Hơn nữa, nó cũng mang tính bao quát hơn : các dữ liệu trong L1/L2 phải xuất hiện trong cả L3. Thậm chí Intel còn đưa ra lý do cho giải pháp này ( hình trên trái tương ứng với Cache dành riêng còn hình bên phải là Cache bao quát – dùng chung ).

Hãy thử phân tích giải pháp đầu tiên:

Nhân 0 yêu cầu dữ liệu từ Cache L3 nhưng không tìm thấy chúng ở đó.

Trong trường hợp bên trái, điều này chẳng có gì cả: những dữ liệu này có thể được lưu trong Cache L1/L2 của các nhân khác. Cache dùng chung loại trừ tình huống này, vì thế không cần phải kiểm tra thêm.

Hãy thử phân tích một tình huống khác:

Nhân 0 yêu cầu dữ liệu từ cache L3, và thực sự là dữ liệu này được chứa ở đây. Cache riêng biệt chẳng gặp vấn đề gì ở đây: nếu dữ liệu nằm trong cache L3 thì chúng chẳng còn nằm ở đâu khác. Còn Cache dùng chung lại gặp một vấn đề: dữ liệu phải nằm trong L1/L2 của một trong các nhân. Nhưng là nhân nào?

Việc này không thành vấn đề với Nehalem: mỗi dòng trong Cache L3 chứa các bit hợp lệ trong nhân ( dựa theo số nhân vật lý), chúng biểu hiện việc dữ liệu L1/L2 gốc được chứa trong nhân nào. Vì thế không cần phải dò tìm từng nhân.

Intel cũng có một ý tưởng tương tự về cấu trúc Cache tối ưu: tốc độ quan trọng hơn dung lượng . Việc này có thể liên quan đến thực tế là họ có rất nhiều lợi thế trong việc thiết kế Cache với dung lượng lớn vì công nghệ chế tạo Transistor là 45nm. Tuy nhiên hơi thất vọng một chút về việc Cache L3 trong Core i7 không hoạt động theo tốc độ xung nhịp của bộ vi xử lý, mà theo một tốc độ cố định .Tuy nhiên, có hai điều giúp bù lại sự thất vọng này: một là L3 trong AMD Phenom cũng hoạt động ở một tốc độ cố định; và thứ hai là tốc độ này vẫn cao hơn trong Core i7 (2.66 GHz).

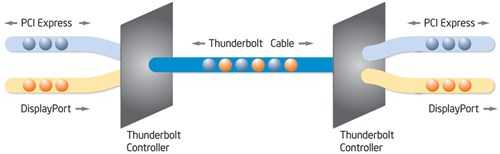

QPI thay thế cho QPB

Tiêu đề này nghe có vẻ lạ tai nhưng thực ra lại rất phù hợp: QPIchữ viết tắt của Bus bộ vi xử lý mới của Intel (QuickPath Interconnect)chỉ khác với Bus cũ QPB (Quad Pumped Bus)một chữ cái hay còn được gọi là FSB .

Vậy thì QPI là gì? Về mặt kỹ thuật thì đây là một Bus 20-bit 2 chiều với phương thức truyền dữ liệu từ điểm-tới-điểm ( Point-to-Point ), mỗi mỗi hướng là mang dữ liệu 16-bit, 4 bit còn lại dùng cho việc sửa lỗi và giao thức. Với khả năng xử lý 6.4 tỉ giao dịch mỗi giây, QPI có tốc độ trao đổi dữ liệu lên 12.8 GB/giây theo mỗi hướng, tổng cộng là 25.6 GB/giây. Vì thế đây là Bus xử lý nhanh nhất (1600-MHz QPB có tổng băng thông là 12.8 GB/giây, AMD HyperTransport 3.0 — 24 GB/giây). Tuy nhiên, phiên bản QPI nhanh nhất hiện mới chỉ dành cho Core i7 Extreme Edition. Còn các bộ xử lý Core i7 bình thường thì chậm hơn một chút với băng thông là 4.8 tỉ giao dịch mỗi chu kỳ.

Lý do ở đây là: lượng băng thông chỉ dùng như vậy vì trong hầu hết thời gian sử dụng bộ vi xử lý để bàn, thì Bus QPI chỉ dùng để kết nối với Chipset mà thôi , bởi khi đó mạch điều khiển bộ nhớ đã được tích hợp vào bộ xử lý. (Giải pháp này chỉ hữu ích khi chipset cung cấp thật nhiều đường truyền PCI Express 2.0, giống như trong chipset Intel X58 dành cho Nehalem.)

Vì thế rõ ràng là QPI được thiết kế dành cho những ứng dụng hoàn toàn khác mà bạn có thể xem trong hình trên. Những bộ xử lý với cấu trúc mới được thiết kế riêng cho máy chủ sẽ chứa một số mạch điều khiển QPI để kết nối trực tiếp với nhau nhằm thực thi tối ưu cấu trúc bộ nhớ NUMA (Truy cập bộ nhớ không đồng nhất – Non-Uniform Memory Access ). Cách làm này được áp dụng rộng rãi trong nhiều nền tảng máy chủ .

Do đó, các bản Core i7 dành cho máy chủ cũng tương tự với AMD Opteron về cấu trúc hình học Topology. Điều này cũng tốt thôi, bởi các nhà thiết kế phần mềm máy chủ cuối cùng cũng có được câu trả lời cho câu hỏi rằng cần phải tối ưu hóa ứng dụng của họ cho cấu trúc bộ nhớ nào. Tuy nhiên điều này chỉ đúng đối với máy chủ. Còn với máy tính để bàn thông thường, bạn sẽ khó mà nhận ra lợi thế nào của QPI.

Quản lý điện năng

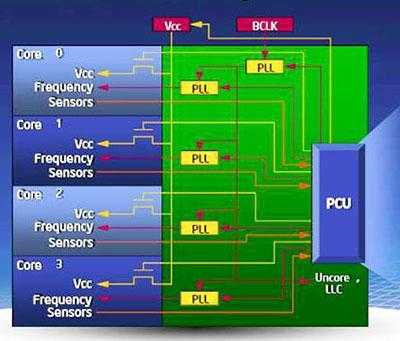

Nehalem đã quá chú ý đến việc quản lý điện năng như thể Intel là người đầu tiên nhìn thấy trước cuộc khủng hoảng kinh tế vậy. Cấu trúc này thực hiện việc quản lý điện năng theo cách truyền thống: toàn bộ cấu trúc quản lý điện được đưa vào một bộ phận riêng gọi là PCU (Bộ phận Quản lý Điện năng – Power Control Unit ). Nó có vai trò như một bộ xử lý thô sơ bên trong một bộ xử lý.

Và bộ xử lý Mini này hỗ trợ một quy trình quản lý phức tạp hơn nhiều so với các bộ xử lý khác của Intel: xung nhịp và điện áp của mỗi nhân được điều khiển riêng biệt dựa trên thông tin về nhiệt độ và lượng điện tiêu thụ. Do đó mỗi nhân có thể chuyển riêng sang mức tiêu thụ điện thấp. Mạch điều khiển bộ nhớ và Bus QPI sẽ chuyển sang chế độ điện năng thấp khi tất cả các nhân đều nghỉ.

Thực ra AMD cũng làm điều tương tự với công nghệ Cool’n’Quiet 2.0 (Phenom),chỉ khác ở chỗ C’n’Q 2.0 cho phép một bộ vi xử lý tương tác với Bộ chuyển đổi năng lượng tích hợp trên Motherboard, trong khi bộ phận quản lý điện của Nehalem thì được tích hợp hoàn toàn vào trong CPU và không đòi hỏi (hoặc cho phép) các thiết bị bổ sung khác.

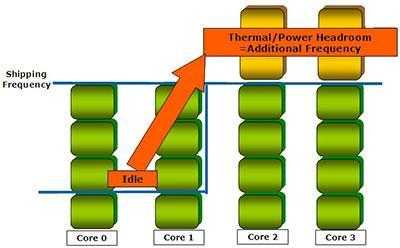

Turbo Boost

Intel đang dần dần thực hiện ý tưởng overclocking một cách vững chắc: đầu tiên chức năng overclock chỉ xuất hiện trong bo mạch chủ, giờ đây nó đã được đưa vào cả bộ xử lý. 🙂 Nghiêm túc mà nói thì chính CPU của Nehalem đã cho phép thực hiện một tính năng thú vị khác: bộ xử lý này có thể tăng xung nhịp của một hoặc một vài nhân nếu các nhân khác đang nghỉ. Theo các hiểu này thì có hai tùy chọn Turbo: tăng xung nhịp của vài nhân lên một bước (+133 MHz) và tăng xung nhịp của một nhân lên 2 bước (+266 MHz). Các nhân khác không cần ở chế độ nghỉ: Turbo Mode sẽ thực hiện khi mức sử dụng nhân cho phép tăng xung nhịp trong một số nhân mà không vượt quá mức TDP tối đa. Ngoài ra còn có một tính năng tặng thêm khác — Turbo Boost, cũng như trong PCU, không liên quan gì đến hỗ trợ ngoài, tức là nó hoạt động trong một bộ xử lý và không cần có thêm phần mềm hoặc phần cứng phụ trợ nào.